Pfad: Home Speicher und Cache

|

| 2-3-2-6 Timing | CAS-Latency: 2 Takte RAS-to-CAS: 3 Takte RAS Precharge: 2 Takte Active to Precharge: 6 Takte |

Der Speicherzugriff erfolgt Matrix-artig in zwei Stufen: zuerst die Zeilen addressiert, danach die Spalten.

Bevor nach der Aktivierung eines Speicherchip durch "Chip Select" (CS) das Spalten-Signal (RAS = Row Address Strobe) aktiviert werden kann, vergeht eine "Command Rate" von typischerweise 1-2 Takten. Bevor die Zeile tatsächlich aktiv ist (Aktive Row) und auf die Spalten (Columns) zugegriffen werden kann, muß die 2 oder 3 Takte (RAS-to-CAS-Delay) vergehen. Nach dem Lesebefehl vergehen bei DDR-Speichern 2, 2,5 oder 3 Takte (CAS Latency), bevor die Daten am Datenbus gültig sind. Die Aktiv-Phase einer Zeile darf eine Mindestdauer nicht unterschreiten (Active to Precharge Delay). Die Deaktivierung nach dem Lesezugriff dauert z.B. 2 Takte (RAS Precharge Time). Mit dem "Write Enable"-Signal (WE) bestimmt der Speicher-Controller, ob es sich um einen Lese- oder Schreibzyklus handelt.

Der Einfluß des Speichertimings auf die Gesamtperformance war zu Zeiten von SDR SDRAM gravierender als bei modernen DDR-Speicher. Der Mehrpreis für schnelleres Timing macht sich höchstens bei rechenintensiven Aufgaben wie Packen/Encoden bemerkbar. (siehe auch: Toms Hardware Guide).

Vom DRAM zum SDRAM

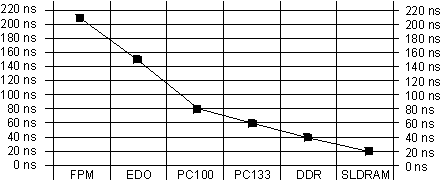

Alle Speicherchips verfügen über eine feste Latenz-Zeit (Pausenzeit); sie beträgt bei aktuellen Chips zwischen 40 und 60 Nanosekunden für die erste Leseoperation.

Der wesentliche Unterschied zwischen SDRAM und DRAM liegt in der Behandlung der danach folgenden Lesezugriffe. Im FPM-RAM (Fast Page Mode) wird die Column-Adresse mehrmals weitergeschaltet, um auf die nächste Zelle zu zeigen. Danach geht CAS auf Null, und nur dann lassen sich die Daten übertragen.

EDO (Extended Data Out) unterscheidet sich insofern davon, daß schon während des Weiterschaltens die Daten transferiert werden. Damit überlagern sich die Zyklen etwas.

SDRAM wiederum besteht intern aus zwei Bänken, wobei die zweite Bank geladen wird (RAS- und CAS-Aktivierung), während aus der ersten Bank die Daten übertragen werden. Diesen Vorgang nennt man auch Interleaving.

Speichertypen (SRAM, FPM, EDO, SDRAM, VCM, RDRAM, DDR)

Static RAM (SRAM) und Dynamic RAM (DRAM)

Grundsätzlich gibt es lediglich zwei Speichertypen: SRAM (statischer RAM) und DRAM (dynamischer RAM). Dynamisch bedeutet, daß der Speicher seinen Inhalt nur sehr kurze Zeit behält und dann wieder aufgefrischt werden muß. Das liegt daran, daß die einzelnen Bits in Kondensatoren gespeichert sind. Im statischen RAM hingegen wird der aktuelle Zustand in Kippstufen oder Flip-Flops gespeichert, einer Schaltung von mehreren Transistoren, die einen Zustand solange beibehält, bis die Schaltung durch ein Signal gekippt wird. SRAM ist daher generell wesentlich schneller als DRAM, aber auch sehr viel teurer; er findet sich daher nur in Cachespeichern, während der Hauptspeicher auf DRAM basiert. DRAM-Typen sind z.B. FPM, EDO und SDRAM.

Fast Page Mode (FPM)

Die klassischen Speicherchips nutzen FPM. Sie gibt es mit 60 oder 70 ns Zugriffszeit. Bei einem Pentium-Mainboard mit 66 MHz Systemtakt sollte man 60 ns Typen verwenden, in der Praxis laufen die 70 ns Typen meistens jedoch auch stabil. Der sogenannte VRAM oder Video-RAM auf älteren Grafikkarten ist nicht viel anders, jedoch mit teilweise schnelleren Zugriffszeiten (bis hinab zu 48 ns) und zweifachen Port, d.h. CPU und RAMDAC können gleichzeitig auf den Speicher zugreifen ohne aufeinander warten zu müssen. "Fast Page Mode" bedeutet, daß das Modul "hofft", daß der nächste Zugriff im gleichen Speicherabschnitt (ROW) stattfindet, damit der Zugriff schneller gelingt. Der schnellste Zugriff in CPU-Zyklen beträgt hier 5-3-3-3 für einen Burst von 4 Daten (Byte / Word / Dword).

Extended Data Output (EDO) DRAM

EDO-RAM unterscheidet sich gegenüber FPM in einer Änderung des Timings zwischen CAS#-Signal und Datenausgabe mit Hilfe eines Latches. Hierdurch werden sequentielle Lesezugriffe beschleunigt. Schreibzugriffe bleiben unverändert. Der schnellste Lese-Zugriff in CPU-Zyklen beträgt hier 5-2-2-2. EDO-Module sind bis maximal 66 MHz Systemtakt geeignet. Als Spannungspegel für die Datenleitungen war 5V üblich.

Burst Extended Data Output (BEDO) DRAM

BEDO RAM hat gegenüber EDO-RAM zusätzliche Ausgangsregister und einen internen Zähler. Bei einem Burst-Zugriff wird Speicheradresse zu Beginn geladen und intern hochgezählt, so daß der Zugriff ab dem zweiten Datum nur noch einen Systemtakt erfordert. Der schnellste Lese-Zugriff in CPU-Zyklen beträgt hier 5-1-1-1. BEDO-Module sind bis maximal 66 MHz Systemtakt geeignet und werden z.B. von Intels 440FX- und AMDs 640-Chipsatz unterstützt. BEDO-RAM-Module haben sich jedoch nicht durchgesetzt.

Synchronous DRAM (SDRAM)

Die Ein- und Ausgangssignale werden mit dem Systemtakt synchronisiert, wobei der Systemtakt wesentlich höher als 66 MHz sein darf (PC-66, PC-100, PC-133). Der schnellste Zugriff in CPU-Zyklen beträgt 5-1-1-1. Der Spannungspegel der Datenleitungen beträgt bei SDRAM-Modulen meistens 3,3V.

Double Data SDRAM (DDR SDRAM)

Im Gegensatz zu SDR-SDRAM-Modulen [SDR = Single Data Rate] werden die Daten bei DDR-Speicher nicht nur auf der steigenden, sondern auch auf der fallenden Flanke des Systemtakts übertragen. Damit läuft ein DDR-SDRAM bei einem Bustakt von 100MHz effektiv mit 200 MHz. Bei einer üblichen Datenbusbreite von 64Bit (= 8 Bytes) steigt die theoretisch maximale Datentransferrate (eff. Taktfrequenz mal Datenbusbreite)) gegenüber herkömmlichen SDR-SDRAM von 800 auf 1600 MB/s. Ein komplettes Speichermodul wird entsprechend seiner max. Datentransferrate bezeichnet (z.B. PC1600). Die einzelnen Chips eines Moduls werden entsprechend der DDR-Taktrate bezeichnet, z.B. DDR200 bei 200MHz.

| Bustakt (physikalisch) | Datenbustakt (effektiv) | Speicher-Modul (Bezeichnung) | Datentransferrate (maximal) | DDR-Speicherchips (nach JEDEC) |

| 100 MHz | 200 MHz | PC1600 | 1600 MB/s | DDR200 |

| 133 MHz | 266 MHz | PC2100 | 2100 MB/s | DDR266 |

| 166 MHz | 333 MHz | PC2700 | 2700 MB/s | DDR333 |

| 200 MHz | 400 MHz | PC3200 | 3200 MB/s | DDR400 |

| 266 MHz | 533 MHz | PC4200 | 4200 MB/s | (DDR533) |

Von Intel zertifizierte DDR400-Speicher: http://developer.intel.com/technology/memory/ddr/valid/dram_results.htm

Zur Verbesserung des Gleichklangs von Takt- und Datensignal setzt man ein differenzielles Taktsignal ein; im Vergleich zum massebezogenen Taktsignal bei SDR-SDRAM ist das differenzielle Signal störfester und lässt sich mit höherer Präzision auswerten. Zusätzlich enthält jedes DDR-Speicherchip eine sogenannte DLL-Schaltung (Delay Locked Loop), welche ein DQS-Impuls (Data Strobe Signal) erzeugt, das die Gültigkeit eines Datenworts anzeigt. Die eigentlichen Speicherzellen von DDR-SDRAMs arbeiten nicht schneller als bei SDR-SDRAM, werden aber paarweise angesprochen und dann nacheinander ausgegeben, so daß die doppelte Datenrate möglich wird.

Der Spannungspegel der Datenleitungen beträgt bei aktuellen DDR-SDRAM-Modulen 2,5V. Shuttle bietet diverse Mainboards mit DDR-Speicher-Unterstützung für Sockel370, Sockel A und Sockel478 an.

DDR2-Speichermodule

DDR2 dient als Nachfolgetechnologie zum herkömmlichen DDR-Speicher, ohne jedoch grundsätzlich Neues zu bringen. Jeweils während der steigenden und der fallenden Flanke eines Taktzyklus werden Daten übermittelt, so dass sich eine Verdoppelung der Bandbreite ergibt. DDR2-533 arbeitet beispielsweise mit einem Basistakt von 266 MHz. Zur Berechnung der Bandbreite genügt die Multiplikation von Taktrate und Busbreite (533 x 64). Durch acht geteilt ergibt sich die Bandbreite in Megabyte pro Sekunde. Die folgende Tabelle fasst Speichertypen und deren Bandbreiten zusammen.

| Bustakt (physikalisch) | Datenbustakt (effektiv) | Speicher-Modul | Datentransferrate | Datentransferrate | DDR-Speicherchips |

| 200 MHz | 400 MHz | PC2-3200 | 3.200 MB/s | 6.400 MB/s | DDR2-400 |

| 266 MHz | 533 MHz | PC2-4300 | 4.266 MB/s | 8.533 MB/s | DDR2-533 |

| 333 MHz | 667 MHz | PC2-5300 | 5.333 MB/s | 10.666 MB/s | DDR2-667 |

| 400 MHz | 800 MHz | PC2-6400 | 6.400 MB/s | 12.800 MB/s | DDR2-800 |

Direct Rambus DRAM (DR DRAM oder RDRAM)

Basiert auf einem eigenen Speicherbus von 16 Bit Breite, der auf bis zu 4 Kanäle mit je einem Controller erweitert werden kann. Das Dual-Channel-Interface des i850-Chipsatzes unterstützt theoretisch bis zu 3,2GB/s (1,6 pro Kanal, max. 4 Kanäle sind möglich). Der Spannungspegel der Datenleitungen beträgt bei aktuellen RDRAM-Modulen 2,5V. Jedoch konnte sich RDRAM bisher nicht durchsetzen, u.a. weil das Preis/Leistungs-Verhältnis zu gering ist.

| Speicher-Modul (RDRAM) | Datentransferrate (Dual-Interface) |

| PC800 | 3200 MB/s bei 2x 16 Bit 6400 MB/s bei 2x 32 Bit |

| PC1066 | 4200 MB/s bei 2x 16 Bit 8400 MB/s bei 2x 32 Bit |

| PC1200 | 4800 MB/s bei 2x 16 Bit |

VC SDRAM (Virtual Channel)

Speichertechnologie von NEC. Der Zugriff bei VC-SDRAM auf die eigentlichen Speicherzellen wird über Kanäle gesteuert. Diese Kanäle werden über 16 unabhängige Eingangs-Puffer von je 1kB realisiert, die die internen Vorgänge von der Verbindung mit dem Außenbereich abkoppeln. Dadurch kann man gleichzeitig sowohl interne Vorgänge wie z.B. das Verschieben von Speicherbereichen als auch externe Vorgänge wie Lese-/Schreibzugriffe durchführen.

- Interne und externe Vorgänge stören sich nicht mehr und können so in kürzerer Zeit abgearbeitet werden.

- Über den breiten internen Bus können zudem sehr viele Daten parallel verschoben werden.

- Die Daten können schon für den nächsten Zugriff vorbereitet werden, die mittlere Zugriffszeit verbessert sich.

- Wenn auf einige Teile des VC SDRAM kein interner Zugriff erfolgt, also nur auf die Kanalpuffer, werden diese Teile in einen stromsparenden Schlafmodus versetzt.

Performance-Steigerung: Im Allgemeinen kann man sagen, dass man bis zu 25% mehr Leistung verbuchen kann als bei SDRAM. Beim Test von Anandtech stellte sich jedoch heraus, dass es Situationen gibt, bei denen VC SDRAM langsamer ist, als gewöhnlicher SDRAM. Unterstützt wird VC SDRAM von VIA Apollo Pro Chipsätzen. Der Preis soll nur etwa 5-10% höher liegen als bei PC133 SDRAM, jedoch ist keine Bezugsquelle bekannt.

Zeitangaben bei SDRAM-Speicher

Alle Zeitangaben gelten immer ab einem Clock-Signal. Dieser periodische Takt wird von außen an das SDRAM-Modul herangeführt und hat eine Frequenz von z.B. 100MHz, dies entspricht einer Periodendauer von 10ns. Intern ist braucht das Speichermodul für bestimmte Aktionen festgelegte Mindestzeiten. "SDRAM" bedeutet "Synchrones DRAM", d.h.: alle Operationen laufen mit Systemtakt ab und belegen eine oder mehrere Taktperioden. Dauert eine Aktion 8 Nanosekunden, wird (bei 100MHz) ein Taktzyklus von 10 Nanosekunden benötigt. Sind es 11 Nanosekunden, dann sind zwei Taktzyklen (20 Nanosekunden) nötig. Anders ausgedrückt: Wofür ein DRAM 11 Nanosekunden braucht, benötigt ein SDRAM (mit 100 MHz) 20 Nanosekunden. Benötigt eine Aktion 9 oder 10 Nanosekunden, dann müssen übrigens trotzdem 2 Taktzyklen à 10ns veranschlagt werden, weil das Signal einige Zeit benötigt, um sich zu stabilisieren, damit es nicht in die nächste Periode überschwingt. Deshalb ist für PC-100-Chips eine Zykluszeit von kleiner/gleich 8 Nanosekunden spezifiziert.

Die wichtigsten 5 Timing-Werte für SDRAM lauten:

| t RP | Row Precharge | Zeitraum zum Umschalten der Bänke über die Zeile |

| t RCD | RAS CAS Delay | Zeit, die zwischen dem Anlegen des RAS- und des CAS-Signals vergehen muß |

| t AC | Access Time | Zeitraum, um die Ausgabe im Burst-Modus vorzubereiten |

| t CAC | Column Access | Die erforderliche Spaltenzugriffszeit |

| t RCT | Read Cycle Time | Zeitraum, um die Daten für den nächsten Lesezyklus im Burst-Modus bereitzustellen |

In der Werbung wird meistens nur die Read Cycle Time angegeben. Dieser Parameter gibt die Zeit an, die ein Baustein auf dem DIMM benötigt, um gültige Daten zu liefern. Ein 'echter' PC-100-SDRAM benötigt nur 6 ns für die Bereitstellung der Daten. Intel hat hier allerdings auch eine Einschränkung zugelassen: In PCs mit nur zwei DIMM-Steckplätzen darf diese Zeit 7 ns betragen. Ein SDRAM-Speichermodul mit 8ns-Angabe reicht nicht für die PC-100-Spezifikation. Allerdings sagt dieser Parameter recht wenig über den kompletten Lesezyklus aus.

Unter CAS versteht man die Anzahl der Taktzyklen vom Aktivieren der CAS-Leitung bis zum Schreiben der Daten in den Ausgabepuffer vergehen. Die Anzahl der Takte für die CAS-Latency hängt direkt von der Spaltenzugriffszeit ab. So gibt es viele PC-100 Speichermodule, die zwar bei 66MHz mit CAS 2 funktionieren, jedoch bei 100MHz auf CAS 3 betrieben werden müssen.

Bei Speicherzugriffen wird die meiste Zeit für den Overhead verbraucht und ein verhältnismäßig geringer Teil für den eigentlichen Datentransfer. Im sogenannten Burst-Modus werden vier aufeinanderfolgende 64-Bit-Blöcke (= 32 Byte) im Stück gelesen oder geschrieben. Dabei wird nur die Adresse für den ersten Block übertragen und im Adreßpuffer des DRAM gespeichert. Für die folgenden drei Blöcke wird nur noch weitergeschaltet. Beschrieben wird ein Burst in der Art x-y-y-y. Das X steht für den ersten Zugriff, die Y beschreiben die restlichen Taktzyklen für jedes weitere 32Bit-Datenwort. Bei einem Burst von 4-1-1-1 werden z.B. 7 Taktzyklen benötigt, um 32 Byte zu übertragen.

Zeit zum Lesen von 32 Bytes im Burst Modus

![]()

Druck-Version der Originalseite: http://de.shuttle.com/memtyp.htm

Shuttle Computer Deutschland - Änderungen und Druckfehler vorbehalten. Datum:

30.4.2008