|

Achtung: Die aktuelle

Shuttle-Website finden sie unter http://www.shuttle.com

! Diese Website enthält Archivdaten, deren Aktualität nicht gewährleistet werden kann. |

| Produkte | Support | Index |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Unterkapitel: Spezifikation | Konfiguration | | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

| Systemtakt Frequenz | Jumper JP 13 |

| 60 MHz |

|

| 66 MHz |

|

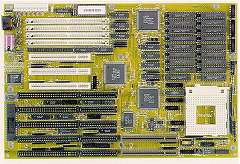

Ansicht: CPU-Sockel untenhalb dieser Jumper

Cache-Speicher Konfiguration

Cache-Speicher Konfiguration

| Cache-Speicher Kapazität | JP21 | JP26 ... JP22 |

| 64 kB |

| |

| 128 kB |

| |

| 256 kB |

| |

| 512 kB |

|

Ansicht: links vom CPU-Sockel JP21, rechts vom CPU-Sockel die anderen Jumper

| Cache-Speicher Kapazität | Daten SRAM | Daten SRAM | Tag SDRAM | Dirty Bit |

| 64 kB | 8k x 8 | leer | 8k x 8 auf U63 | 16k x 1 |

| 128 kB | 8k x 8 | 8k x 8 | 8k x 8 auf U63 | 16k x 1 |

| 256 kB | 32k x 8 | leer | 8k x 8 auf U63 | 16k x 1 |

| 512 kB | 32k x 8 | 32k x 8 | 8k x 8 auf U63, U45 | 16k x 1 |

AT-Bus Takt-Einstellung

AT-Bus Takt-Einstellung

| AT-Bus Takt | JP7 | Systemtakt = 60 MHz | Systemtakt = 66 MHz |

| PCI-Takt / 5 |

| 6.0 MHz | 6.6 MHz |

| PCI-Takt / 4 |

| 7.5 MHz | 8.3 MHz |

| PCI-Takt / 3 |

| 10.0 MHz | 11.0 MHz |

| PCI-Takt / 2 |

| 15.0 MHz | 16.5 MHz |

Quelle des PCI-Taktes

Quelle des PCI-Taktes

Hiermit wird bestimmt, ob der PCI-Takt (LCLK) von einem im U54-Sockel bestückten Quarz-Oszillator generiert wird, oder ob er intern aus dem Systemtakt abgeleitet wird.

| PCI-Takt | JP19 | U54 | JP11 |

| Extern (Standard) |

| Quarz ist bestückt |

|

| Intern |

| Quarz ist nicht bestückt |

|

Vesa Local Bus Konfiguration

Vesa Local Bus Konfiguration

| VL-Bus Konfiguration | JP15 | JP16 |

| PCI-Takt >=33 MHz | x |

|

| PCI-Takt <30 MHz | x |

|

| High Speed Write |

| x |

| High Speed Write |

| x |

| Navigation |

|

|

Shuttle Computer Deutschland +++ Disclaimer +++ Letztes Update: 30.4.2008